ニコン社が2021年ISSCCで新型の積層CMOSイメージセンサを開発したと発表しました。

発表した新型積層CMOSイメージセンサの資料

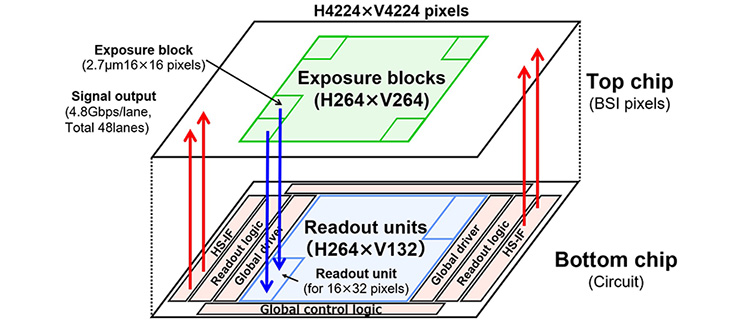

総画素数1784万画素で1000fps、110dB出るイメージセンサを開発したようです。どのようにして高フレームレートとHDRの両立を実現したのか気になりますね。記事では、4224×4224画素を16×16画素を1ブロックとして264×264ブロックに分割し、各ブロックに適した露光時間を設定していると書いてあります。

引用元:ニコン報道資料(https://www.nikon.co.jp/news/2021/0217_cmos_01.htm)

つまり、画面内の明るい部分には長時間露光を適用し、暗い部分には短時間露光を適用することでHDRを実現しているということになります。積層センサであることで、回路面積が大きくなりこのような特殊なセンサを実現することができたんだと思います。一方で、16×16画素の1ブロック内で明暗差が大きい場合はどうなるのでしょうか。おそらく、そのブロックだけ白飛びや黒つぶれが発生するんじゃないかなと考えています。(知っている方は教えてください。。)

まあ、究極的なことを言うと1画素ずつ露光時間を設定できるのが最高のシステムになると思いますが、今回16×16画素で1ブロックにしているのは積層にしても回路面積が足りず16×16でギリギリ回路が入ったってことですかね。製造プロセスの進化や回路の開発、工夫によって、今後1ブロックの画素数はどんどん減ると思うので、今後のニコン社の開発を楽しみにしましょう。

これってきっと、各ブロックが適露光時間を設定されるまでに何フレームかかかるんですかね?少なくとも1フレームは画素値を検出する必要があると思います。もし数フレームかかるのであれば高輝度物体が高速に画面内を移動している場合、露光時間の設定がおかしくなったりしないのでしょうか。(考え方がおかしいですかね?)

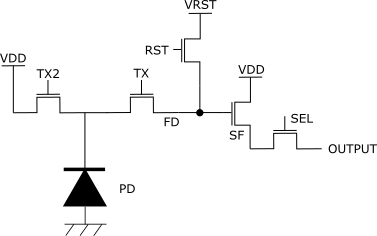

ちなみに画素構造についてですが、通常PDにたまった電荷をすべてFDに転送して電荷を読み出すことをしていると思います。一方今回発表されたセンサは、FDへ行くルートのほかに電荷を捨てるルートを持っているのだと思います。途中まで溜まった電荷を捨てて露光スタート時間を変えることで、露光時間を調節しているのではないでしょうか。

回路図で表すとこんな感じですかね。細かいところは全然違うと思いますが、PDから転送ゲート2を通って電荷を捨てる構造はこんな感じだと思います。PDの不要な電荷を捨てることができるというのは、何度か見たことがあります。

ここまでニコンの新型CMOSイメージセンサについて説明しましたが、今後も進化が楽しみなセンサですね。今後の開発に期待しましょう!

読んでいただきありがとうございます。よろしければぜひブックマークをお願いいたします!

コメント